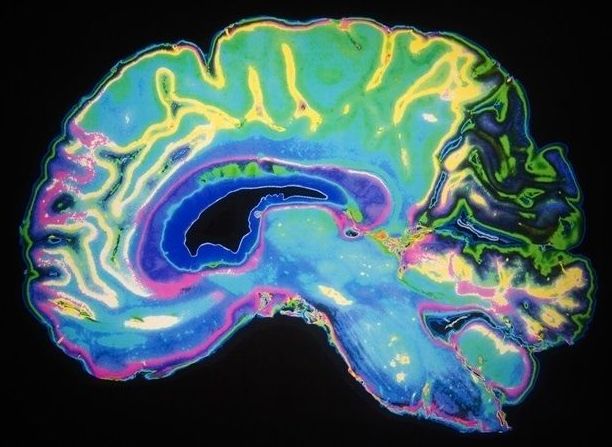

If an unconscious person responds to smell through a slight change in their nasal airflow pattern — they are likely to regain consciousness. This is the conclusion from a new study conducted by Weizmann Institute scientists and colleagues at the Loewenstein Rehabilitation Hospital, Israel. According to the findings, published in the journal Nature, 100% of the unconscious brain-injured patients who responded to a “sniff test” developed by the researchers regained consciousness during the four-year study period. The scientists think that this simple, inexpensive test can aid doctors in accurately diagnosing and determining treatment plans according to the patients’ degree of brain injury. The scientists conclude that this finding once again highlights the primal role of the sense of smell in human brain organization. The olfactory system is the most ancient part of the brain, and its integrity provides an accurate measure of overall brain integrity.

Following severe brain injury, it is often difficult to determine whether the person is conscious or unconscious, and current diagnostic tests can lead to an incorrect diagnosis in up to 40% of cases. “Misdiagnosis can be critical as it can influence the decision of whether to disconnect patients from life support machines,” says Dr. Anat Arzi, who led the research. “In regard to treatment, if it is judged that a patient is unconscious and doesn’t feel anything, physicians may not prescribe them painkillers that they might need.” Arzi commenced this research during her doctoral studies in the group of Prof. Noam Sobel of the Weizmann Institute of Science’s Neurobiology Department and continued it as part of her postdoctoral research at the University of Cambridge’s Department of Psychology.

The “consciousness test” developed by the researchers — in collaboration with Dr. Yaron Sacher, Head of the Department of Traumatic Brain Injury Rehabilitation at Loewenstein Rehabilitation Hospital — is based on the principle that our nasal airflow changes in response to odor; for example, an unpleasant odor will lead to shorter and shallower sniffs. In healthy humans, the sniff-response can occur unconsciously in both wakefulness and sleep.