A recent study published in Communications Earth & Environment examines how lunar samples collected and returned by Apollo astronauts contain traces of hydrogen produced by the solar wind. The samples, labeled 79221, were collected during surface activities on Apollo 17 in 1972, and holds the potential to help scientists and engineers better understand how hydrogen within these samples can be used for future space exploration, specifically pertaining to in-situ resource utilization (ISRU).

The practice of ISRU involves using resources directly available at a location without the need of resupply from an outside source. In this case, future lunar astronauts would want to use resources already present on the Moon for their survivability needs rather than having constant resupply from the Earth, which can be both costly and risky.

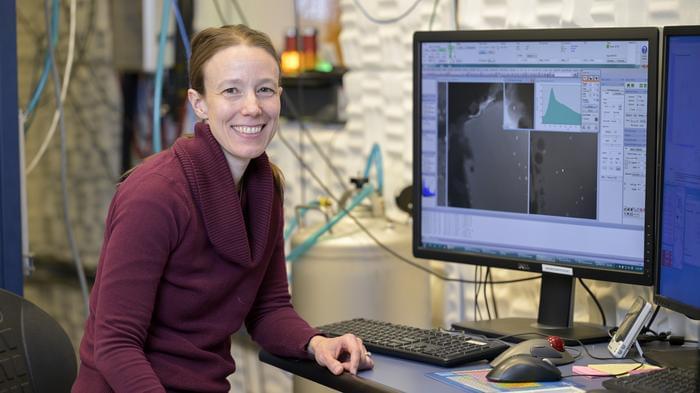

“Hydrogen has the potential to be a resource that can be used directly on the lunar surface when there are more regular or permanent installations there,” said Dr. Katherine D. Burgess, who is a geologist in the U.S. Naval Research Laboratory (NRL) Materials Science and Technology Division and lead author of the study. “Locating resources and understanding how to collect them prior to getting to the Moon is going to be incredibly valuable for space exploration.”