Although we are currently in an era of quantum computers with tens of noisy qubits, it is likely that a decisive, practical quantum advantage can only be achieved with a scalable, fault-tolerant, error-corrected quantum computer. Therefore, development of quantum error correction is one of the central themes of the next five to ten years. Our article “Topological and subsystem codes on low-degree graphs with flag qubits” [1], published in Physical Review X, takes a bottom-up approach to quantum error correcting codes that are adapted to a heavy-hexagon lattice – a topology that all our new premium quantum processors use, including IBM Quantum Falcon (d=3) and Hummingbird (d=5).

Many in the quantum error correction community pursue a top-down computer science approach, i.e., designing the best codes from an abstract perspective to achieve the smallest logical error rate with minimal resource. Along this path, the surface code is the most famous candidate for near-term demonstrations (as well as mid- to long-term applications) on a two-dimensional quantum computer chip. The surface code naturally requires a two-dimensional square lattice of qubits, where each qubit is coupled to four neighbors.

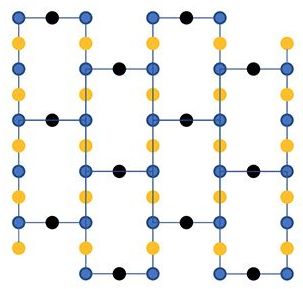

We started with the surface code architecture on our superconducting devices and demonstrated an error detection protocol as a building block of the surface code around 2015 [2]. While the experimental team at IBM made steady progress with cross-resonance (CR) gates, achieving gate fidelities near 99%, an experimental obstacle appeared along the path of scaling up the surface code architecture. The specific way to operate the CR gates requires the control qubit frequency to be detuned from all its neighboring target qubits, such that the CNOT gates between any pair of control and target can be individually addressed.